芝浦工業大学,東京大学,東京農工大学,慶應義塾大学は共同で,電子機器や交通マネーなどに使われるICチップにおいて,演算の必要な場所に必要なときだけ高速で電力供給することで,チップの消費電力を抑える回路設計技術を開発した(ニュースリリース)。

芝浦工業大学,東京大学,東京農工大学,慶應義塾大学は共同で,電子機器や交通マネーなどに使われるICチップにおいて,演算の必要な場所に必要なときだけ高速で電力供給することで,チップの消費電力を抑える回路設計技術を開発した(ニュースリリース)。

コンピュータなどに搭載されるチップ内の素子は,3年で4倍のペースで増大しており,現在は最大規模で約40億個の素子がチップの中に存在している。素子の増加,すなわちチップの高性能化にともない,消費電力が増大するために「高性能化」と「省電力化」を同時に実現する技術が求められている。

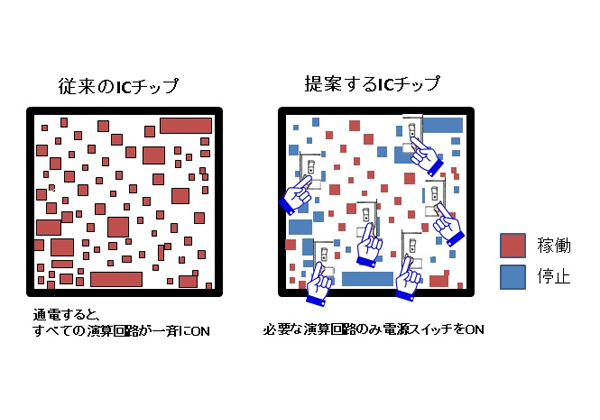

電子機器の省電力化の方法として,チップ内部で通常は遮断状態にしてある回路に対し,使うときだけ通電する「パワーゲーティング:Power Gating(PG)」という技術が知られている。現在コンピュータの世界で応用されている技術としては,例えばマルチコアCPUのうち,稼働が必要なコアのみを効果的に検出し稼働させるCPUコア単位でのPGが一般的だった。

これに対し研究グループは,CPU内部の「演算単位」というさらに細かい粒度でのPGを実現するチップの自動設計技術の開発に成功した。また,すでに自動設計した回路を組み込んだチップを試作して動作確認も行なった。

従来,遮断状態にある演算回路に高速で通電しようとすると,チップ内部で大きな電源ノイズが発生し,回路の誤動作につながる問題があった。そこで今回,チップ内部の電源スイッチの役割を担う素子を細かく分割し,約0.1ナノ秒という時間で少しずつずらしながら通電させることで,電源ノイズの発生を抑えることを可能にした。

この技術を応用し,車の走行や人の運動による振動,太陽光,熱など,身の周りにあるわずかなエネルギーを電力に変換する,環境発電で動作するセンサチップが実用化されれば,電子機器の省電力化だけでなく,建物や橋などの老朽化のモニタリングチップや,位置情報や体調管理などができるウェアラブルチップなどさまざまな分野への応用が期待できるとしている。

関連記事「NEDOら,5mm角の超高速・低消費電力光トランシーバを開発」「NEDOら,シリコンフォトニクスによる低消費電力CPU間高速データ通信技術を開発」「東大,超低消費電力トンネル電界効果トランジスタを開発」