産業技術総合研究所(産総研)は,半導体ICチップの偽造を防ぐ「ICの指紋」を低コスト,高信頼性,コンパクトに実現できる素子とそれを用いた回路技術を開発した(ニュースリリース)。

産業技術総合研究所(産総研)は,半導体ICチップの偽造を防ぐ「ICの指紋」を低コスト,高信頼性,コンパクトに実現できる素子とそれを用いた回路技術を開発した(ニュースリリース)。

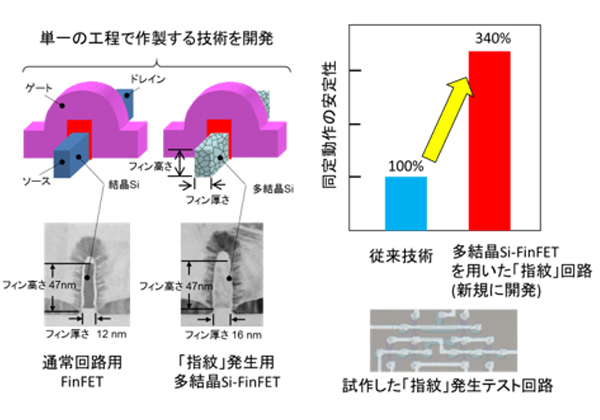

今回開発した「指紋」発生回路は,「指紋」となるICチップの固有番号を,多結晶シリコンFinFETで構成したSRAM回路によって発生する。このSRAM回路の起動時の初期値が0になるか1になるかは,製造時の素子性能のばらつきを反映して決まり,起動ごとに同じ値を示す。

「指紋」発生回路には複数のSRAM回路が用いられ,SRAM回路数のビット数の番号を発生させることができる。個々のSRAM回路の初期値は製造工程でランダムに決まるため,発生した番号はICチップに固有の番号となる。固有番号ビット数を多くすれば同じ固有番号を持つ確率は小さくなるので,そのICチップを複製や偽造できない。

今回,多結晶シリコンFinFETを用いたSRAM回路方式の「指紋」発生テスト回路と,比較のため通常型FinFETで「指紋」発生テスト回路を試作した。

多結晶シリコンFinFET素子とこれを用いた「指紋」発生テスト回路の実験に基づき,128ビット長の「指紋」発生回路において現れる,本来の固有番号と異なるビット(誤りビット)のビット数を見積もった。その結果,平均誤りビット数は,通常型FinFETで作製した回路の3分の1以下に低減することが示唆された。

すなわち,多結晶シリコンFinFETを用いた「指紋」発生回路は通常型FinFETの回路の3倍以上の安定性で固有番号を発生でき,高い確度でICチップの認証や同定ができる。

通常型FinFETの回路で128ビットの固有番号を同等の安定性で発生させる場合にくらべ,多結晶シリコンFinFETの導入によって,少なくとも約15,000トランジスタ分の回路を省略できると見積もられる。これは,22nmテクノロジー換算で,約1,100 μm2の面積縮小に相当する。

さらに,従来の多結晶シリコン薄膜トランジスタ技術とは異なり,低コストで集積回路化が可能。「指紋」の発生に用いられる多結晶シリコンFinFETは,作製工程の初期段階にIC基板の一部に多結晶シリコン薄膜を堆積させた後,標準的なFinFET素子と同一の製造工程で同時に形成されるため,工程が短く終了し,低コスト化につながる。

また回路構成の観点からは,半導体メモリーの1つであるSRAM回路によって「指紋」を発生させることによって,製造工程の条件が変化した場合でも発生される固有番号に偏りが生じない。

今後は,製造工程の後工程で認証用回路のトランジスタを挿入する,デバイスレベル三次元構造への適用を検討していくという。これにより,トランジスタ製造を外注した際に生ずる,固有番号の第三者への漏洩の危険性を低減できるほか,コストの最適化が期待されるとしている。

また,今後盛んになるであろうIoTの端末への適用技術を開発していく。

関連記事「三菱電機ら,LSIの個体差を活用した「指紋認証」のようなセキュリティ技術を開発」「NEC,製品固有の「物体指紋」を認識して個体識別を行なう技術を開発」