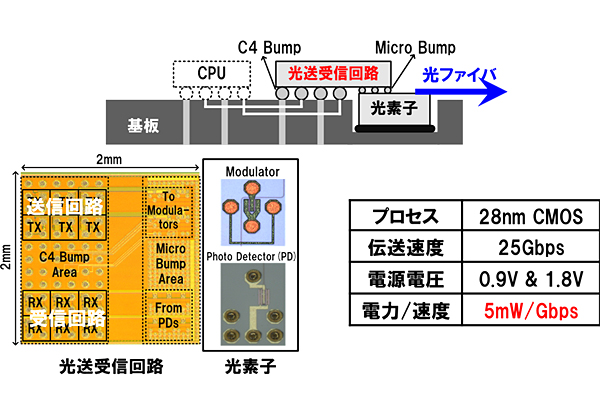

新エネルギー・産業技術総合開発機構(NEDO),技術研究組合光電子融合基盤技術研究所(PETRA),富士通,富士通研究所,Fujitsu Laboratories of America, Inc.は,サーバやスパコンのCPU間高速データ通信を世界最高の電力効率である1Gb/sあたり5mWで実現するシリコンフォトニクス技術を用いた光送受信回路を開発した(ニュースリリース)。

新エネルギー・産業技術総合開発機構(NEDO),技術研究組合光電子融合基盤技術研究所(PETRA),富士通,富士通研究所,Fujitsu Laboratories of America, Inc.は,サーバやスパコンのCPU間高速データ通信を世界最高の電力効率である1Gb/sあたり5mWで実現するシリコンフォトニクス技術を用いた光送受信回路を開発した(ニュースリリース)。

サーバやスパコンは,CPU単体の演算性能を高めるだけでなくCPU間のデータ通信速度の向上も必要とされている。サーバやスパコンではシステム全体で大きな電力を必要とするが,設備が供給できる電力の制約もあるため,データ送受信回路の電力を増やすことなく通信速度を向上させることが求められている。

そこでNEDOは,情報通信機器の省電力化と高速化を目的に,シリコンフォトニクス技術を用いた基盤技術を確立することを目指し,「超低消費電力型光エレクトロニクス実装システム技術開発」プロジェクトを推進している。プロジェクトは今回,光素子を低電圧駆動させながら,送信データの変化を捉えて大きな振幅になるように補い,従来の半分の電力で25Gb/sの高速動作を実現した。

具体的にはCPUからの送信信号が-1や+1に変化するタイミングに限定して増幅することで,1.8V程度の振幅を断続的に発生させることに成功した。これにより,電源電圧が1.8Vと一般的に用いられている3.3Vに比べて低く,データが変化しないところは小振幅で電力を使わないため,低消費電力を実現している。

原理的には,送信データとそれを遅延させたデータを-α(0<α<1)倍したものを足し合わせることで,送信データが-1から+1へ変化する場合,+1が+1+αに増幅される。また,送信データが+1から-1へ変化する場合,-1が-1-αとマイナス方向にさらに変化させることが出来まる。この技術により,高速化と低消費電力化の両立が可能であり,25Gb/sの高速伝送を従来の半分である1Gb/sあたり5mWで実現できることを確認した。

この技術により,消費電力を抑えながら,複数の光送受信回路を並べた毎秒テラビット級の高速伝送を実現できるため,サーバやスパコンの高性能化が期待されるとしている。

関連記事「NTT,シリコンフォトニクスを用いて100ビットを超える光ランダムアクセスメモリを開発」「富士通,多並列化が可能な光送受信回路を開発」