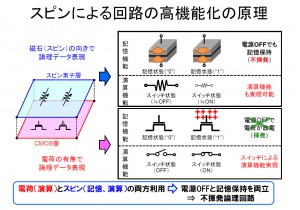

東北大学とNECは,電子機器の待機電力ゼロに向けたスピントロニクス技術を論理集積回路に導入し,論理回路とメモリを一体化した不揮発性ロジックインメモリ集積回路を自動設計できるライブラリを開発した。また,このライブラリを利用して,画像処理用のプロセッサを設計・試作し,演算時に不要な消費電力を1/4に削減できることを実証した。

研究グループは,従来から汎用検索集積回路(TCAM),FPGA用の論理演算回路(LUT),加算器回路など,少ない数のMTJ素子を規則的に並べる回路や回路部品で動作実証を行なってきた。しかし,大規模な論理集積回路は,多数のMTJ素子を複雑・不規則に並べるものが多く,実現のためには不揮発性ロジックインメモリで使用できる自動設計ツールが必要であった。

今回開発したライブラリは,CADを用いた既存の論理回路設計ツールに追加搭載して利用するもので,回路の設計やスピントロニクス技術の専門家でなくても,大規模なロジックインメモリ集積回路の設計が可能になる。

不揮発性ロジックインメモリ集積回路は,論理演算を実施するたびに,演算に不要な回路の電源を切ることができる。これにより,待機電力ゼロ,省電力動作,瞬時な起動を可能にする電子機器を実現できる。

詳しくはこちら。